以规则形状的 SMD(Surface Mounted Devices,表贴器件)的制作为例。

制作焊盘

查看芯片手册中的封装参数;

打开 Pad Designer 新建焊盘文件(.pad);

设置焊盘参数:

Parameters:设置“Units”(单位)和“Decimal places”(精度)。一般,单位为 Mils 时精度最高为 2,单位为 Millimeter 时精度最高为 4。

Layers:制作表贴焊盘需要勾上“Single layer mode”,并设置三个 Layer:

- BEGIN_LAYE;

- SOLDERMASK_TOP(表示这部分在制板时不涂绿油,从而给焊盘开窗,保证焊盘裸露,是实际上允许焊接的区域);

- PASTEMASK_TOP(表示焊接时这个区域要涂焊锡,用于机器焊接)的参数。

注:

表贴类不用填“Thermal Relief ”和“Anti Pad”

一般,“PASTEMASK_TOP”的参数和“BEGIN_LAYER”相同,“SOLDERMASK_TOP”比前面两者大 0.1mm

制作封装

放置焊盘

打开 PCB Editor ,”Drawing Type”选择”Package symbol”,新建封装文件(.dra);

适当修改grids;

添加焊盘文件目录 Setup - User Preferences - Catagories - Paths - Library - 添加上面焊盘所在的目录到 padpath、psmpath、devpath;

添加焊盘引脚 Layout - Pins - 选Connect - 从Padstack中选择焊盘。

画封装

封装包括(红色加粗为必须,斜体为强烈推荐):

至少一个引脚(即焊盘);

图形边框(即 Package Geometry 类中的 Assembly_Top 子类和 Silkscreen_Top 子类),标明1号管脚;

参考编号(即 Ref Des 类中的中的至少一个子类,通常使用 Silkscreen_Top 子类 ,有时顺便画上 Assembly_Top 子类),放在封装的附近;

安装区(即 Package Geometry 类中的 Place_Bound_Top 子类);

保存后会得到

.dra文件(绘图文件,可以打开对封装进行编辑);

.psm文件(数据文件,不能直接编辑,但是在.brd 文件中导入网表时要用到)。

注:

Assembly_Top 上画装配时的外框;

Silkscreen_Top上画丝印图案;

Place_Bound_Top上画一个没有电气规则的区域,防止器件重叠;

将 pad、via 和器件封装的各类文件(.dra和.psm)都存放在同一个文件夹中,方便导入网表、调用及修改。

导入

创建电路板

打开 PCB Editor ,”Drawing Type”选择”Board”,新建电路板文件(.brd),设置图纸尺寸和栅格点大小;

画PCB外框:Add - Line,class选Board Geometry,subclass选Outline;

画允许布线的区域Route Keepin:Setup - Areas - Route Keepin,建议距离外框 30~40mil;

画允许摆放器件的区域Package Keepin:Edit - Z-copy - Size: Contract - Offset: 1,一般将Package Keepin比Route Keepin缩进 1mil 的距离;

放置安装孔,令安装孔与Package Keepin的线框相切。

设置层叠结构

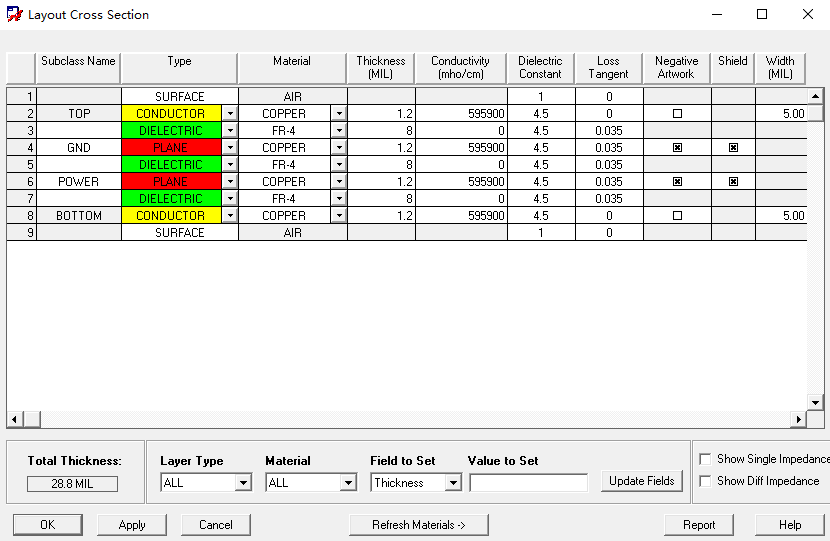

以4层板为例,从上到下依次为:

- TOP(顶层走线层);

- GND(地层铜平面);

- POWER(电源层铜平面);

- BOTTOM(底层走线层)。

Setup - Cross-section - 添加中间的层;

设置各层类型(CONDUCTOR用于走线层,DIELECTRIC为介质层,PLANE为铜平面,用于电源层和地层);

给各层命名;

设置正负片(走线层为正片,即画出来的是要保留的部分;铜平面为负片,即画出来的是要挖掉的部分)。

内电层铺铜

在画了Route Keepin的前提下,使用Z-copy进行内电层铺铜。此时的内电层铺铜只是临时性的,为了方便查看后续布线时过孔是否距离过近。和板外框的调整一样,当布局布线确定后,内电层铜平面也要重新调整(即重新铺铜)。

在Options里选GND或POWER(分别为GND层和POWER层铺铜),选中Create dynamic shape(防止短路);

设置GND层Offset为0,POWER层Offset为40mil(电源层比地层缩进40mil以减少板边缘的对外辐射);

在Find里选中Shapes;

在Visibility里关掉其余内电层的显示(这样在铺铜时可以清楚地看到铺铜是否成功)。

也可以直接在GND层和POWER层铺动态铜,然后合并和调整铜皮形状。

导入网表

File - Import - Logic - Design entry CIS (Capture) - Import directory - Import Cadence

若有文本窗口弹出,根据报错修改后再重新导入;没有窗口弹出说明导入成功。

评论